Fonctionnement d'un ordinateur/Les mémoires RAM dynamiques (DRAM)

Les mémoires RAM dynamiques sont opposées aux mémoires RAM statiques. Les RAM statiques sont les plus intuitives à comprendre : elles conservent leurs données tant qu'on ne les modifient pas, ou tant que l’alimentation électrique est maintenue. Les RAM dynamiques ont pour défaut que les données s'effacent après un certain temps, en quelques millièmes ou centièmes de secondes si l'on n'y touche pas. En conséquence, il faut réécrire chaque bit de la mémoire régulièrement pour éviter qu'il ne s'efface. On dit qu'on doit effectuer régulièrement un rafraîchissement mémoire.

La mémoire principale de l'ordinateur, la fameuse mémoire RAM, est actuellement une mémoire dynamique sur tous les PC actuels. Le rafraîchissement prend du temps, et a tendance à légèrement diminuer la rapidité des mémoires dynamiques. Mais en contrepartie, les mémoires dynamiques ont une meilleure capacité, car leurs bits prennent moins de place, utilisent moins de transistors.

L'interface des DRAM et le contrôleur mémoire

[modifier | modifier le wikicode]Un point important est que les DRAM modernes ne sont pas connectées directement au processeur, mais le sont par l'intermédiaire d'un contrôleur mémoire externe. Le contrôleur mémoire sert d'intermédiaire, d'interface entre la DRAM et le processeur. Il ne faut pas le confondre avec le contrôleur mémoire interne, placé dans la mémoire RAM, et qui contient notamment le décodeur. Les deux sont totalement différents, bien que leur nom soit similaire.

Le contrôleur mémoire est reliée au CPU par un bus, et est connecté aux barrettes ou boitiers de DRAM via le bus mémoire proprement dit. Les anciens contrôleurs mémoire étaient des composants séparés du processeur, du chipset ou du reste de la carte mère. Par exemple, les composants Intel 8202, Intel 8203 et Intel 8207 étaient des contrôleurs mémoire pour DRAM qui étaient vendus dans des boitiers DIP et étaient soudés sur la carte mère. Par la suite, ils ont été intégré au chipset de la carte mère pendant les décennies 90-2000. Après les années 2000, ils ont été intégrés dans les processeurs.

Le contrôleur mémoire externe

[modifier | modifier le wikicode]Le contrôleur mémoire gère le bus mémoire et tout ce qui est envoyé dessus. Il envoie des commandes aux barrettes de mémoire, commandes qui peuvent être des lectures, des écritures, ou des demandes de rafraichissement, parfois d'autres commandes. La mémoire répond à ces commandes par l'action adéquate : lire la donnée et la placer sur le bus de données pour une commande de lecture, par exemple.

Il est possible de connecter plusieurs barrettes sur le même bus mémoire, ou alors celles-ci sont connectées au contrôleur mémoire avec un bus par barrette/boitier. C'est ce qui permet de placer plusieurs barrettes de mémoire sur la même carte mère : toutes les barrettes sont connectées au contrôleur mémoire DRAM d'une manière ou d'une autre. Notons que le contrôleur mémoire est presque toujours un circuit synchrone, cadencé par une horloge, comme le processeur. Et ce peu importe que les mémoires DRAM soient elles-mêmes synchrones ou au contraire asynchrones (sans horloge).

Le rôle du contrôleur mémoire varie grandement suivant le contrôleur en question, ainsi que selon le type de DRAM. Par exemple, les contrôleurs mémoires des toutes premières DRAM ne géraient pas du tout le rafraichissement mémoire, qui était géré par le processeur. Par exemple, le processeur Zilog Z80 implémentait des compteurs pour gérer le rafraichissement mémoire. D'autres processeurs avaient des interruptions dédiées pour gérer le rafraichissement mémoire. Mais les contrôleurs mémoires modernes gèrent le rafraichissement mémoire de manière automatique.

Le bus d'adresse des DRAM est multiplexé

[modifier | modifier le wikicode]Un point important pour le contrôleur mémoire est de transformer les adresses mémoires fournies par le processeur, en adresses utilisables par la DRAM. Car les DRAM ont une interface assez spécifique. Les DRAM ont ce qui s'appelle un bus d'adresse multiplexé. Avec de tels bus, l'adresse est envoyée en deux fois. Les bits de poids fort sont envoyés avant les bits de poids faible. On peut ainsi envoyer une adresse de 32 bits sur un bus d'adresse de 16 bits, par exemple. Le bus d'adresse contient alors environ moitié moins de fils que la normale.

Pour rappel, l'avantage de cette méthode est qu'elle permet de limiter le nombre de fils du bus d'adresse, ce qui très intéressant sur les mémoires de grande capacité. Les mémoires DRAM étant utilisées comme mémoire principale d'un ordinateur, elles devaient avoir une grande capacité. Cependant, avoir un petit nombre de broches sur les barrettes de mémoire est clairement important, ce qui impose d'utiliser des stratagèmes. Envoyer l'adresse en deux fois répond parfaitement à ce problème : cela permet d'avoir des adresses larges et donc des mémoires de forte capacité, avec une performance acceptable et peu de fils sur le bus d'adresse.

Les bus multiplexés se marient bien avec le fait que les DRAM sont des mémoires à adressage par coïncidence ou à tampon de ligne. Sur ces mémoires, l'adresse est découpée en deux : une adresse haute pour sélectionner la ligne, et une adresse basse qui sélectionne la colonne. L'adresse est envoyée en deux fois : la ligne, puis la colonne. Pour savoir si une donnée envoyée sur le bus d'adresse est une adresse de ligne ou de colonne, le bus de commande de ces mémoires contenait deux fils bien particuliers : les RAS et le CAS. Pour simplifier, le signal RAS permettait de sélectionner une ligne, et le signal CAS permettait de sélectionner une colonne.

Si on a deux bits RAS et CAS, c'est parce que la mémoire prend en compte les signaux RAS et CAS quand ils passent de 1 à 0. C'est à ce moment là que la ligne ou colonne dont l'adresse est sur le bus sera sélectionnée. Tant que des signaux sont à zéro, la ligne ou colonne reste sélectionnée : on peut changer l'adresse sur le bus, cela ne désélectionnera pas la ligne ou la colonne et la valeur présente lors du front descendant est conservée.

Le rafraichissement mémoire

[modifier | modifier le wikicode]La spécificité des DRAM est qu'elles doivent être rafraichies régulièrement, sans quoi leurs cellules perdent leurs données. Le rafraichissement est basiquement une lecture camouflée. Elle lit les cellules mémoires, mais n'envoie pas le contenu lu sur le bus de données. Rappelons que la lecture sur une DRAM est destructive, à savoir qu'elle vide la cellule mémoire, mais que le système d'amplification de lecture régénère le contenu de la cellule automatiquement. La cellule est donc rafraichie automatiquement lors d'une lecture.

Les DRAM à rafraichissement externe et pseudo-statiques

[modifier | modifier le wikicode]Sur la quasi-totalité des DRAM, modernes comme anciennes, le rafraichissement est géré par le processeur ou le contrôleur mémoire. Le rafraichissement est déclenché par une commande de rafraichissement, provenant du processeur ou du contrôleur mémoire. Une commande de rafraichissement est un troisième type d'accès mémoire, séparé de la lecture ou de l'écriture, qui n’existe que sur les DRAM de ce type.

Une commande de rafraichissement ordonne de rafraichir une adresse, parfois une ligne complète. Dans le premier cas, le rafraichissement se fait adresse par adresse, on doit préciser l'adresse à chaque fois. Le second cas est spécifique aux mémoires à tampon de ligne, organisées en lignes et colonnes. La lecture d'une ligne la rafraichit automatiquement, ce qui fait qu'il suffit de d'adresser une ligne, pas besoin de préciser la colonne. Les commandes sont donc plus courtes.

Enfin, un dernier cas permet d'envoyer des commandes de rafraichissement vides, qui ne précisent ni adresse ni numéro de ligne. Pour cela, la mémoire contient un compteur, qui pointe sur la prochaine ligne à rafraichir, qui est incrémenté à chaque commande de rafraichissement. Une commande de rafraichissement indique à la mémoire d'utiliser l'adresse dans ce compteur pour savoir quelle adresse/ligne rafraichir.

Il existe des mémoires qui sont des intermédiaires entre les mémoires SRAM et DRAM. Il s'agit des mémoires pseudo-statiques, qui sont techniquement des mémoires DRAM, utilisant des transistors et des condensateurs, mais qui gèrent leur rafraichissement mémoire toutes seules. Le rafraichissement mémoire est alors totalement automatique, ni le processeur, ni le contrôleur mémoire ne devant s'en charger. Le rafraichissement est purement le fait des circuits de la mémoire RAM et devient une simple opération de maintenance interne, gérée par la RAM elle-même.

L'impact du rafraichissement sur les performances

[modifier | modifier le wikicode]Le rafraichissement mémoire a un impact sur les performances. L'envoi des commandes de rafraichissement entre des lectures/écritures fait qu'une partie du débit binaire de la mémoire est gâché. De même, ces commandes doivent être envoyées à des timings bien précis, et peuvent entrer en conflit avec des lectures ou écritures simultanées.

L'envoi des commandes de rafraichissement peuvent se faire de deux manières : soit on les envoie toutes en même temps, soit on les disperse le plus possible. Le premier cas est un rafraichissement en rafale, le second un rafraichissement étalé. Le rafraichissement en rafale n'est pas utilisé dans les PC, car il bloque la mémoire pendant un temps assez long. Le rafraichissement étalé est étalé dans le temps, ce qui permet des accès mémoire entre chaque rafraichissement de ligne/adresse. Les PC gagnent en performance avec le rafraichissement étalé. Mais les anciennes consoles de jeu gagnaient parfois à utiliser eu rafraichissement en rafale. En effet, la mémoire était souvent effacée entre l'affichage de deux images, pour éviter certains problèmes dont on ne parlera pas ici. Le rafraichissement de la mémoire était effectué à ce moment là : l'effacement rafraichissait la mémoire.

Le temps mis pour rafraichir la mémoire est le temps mis pour parcourir toute la mémoire. Il s'agit du temps de balayage vu dans le chapitre sur les performances d'un ordinateur. Concrètement, il est défini en divisant la capacité de la mémoire par son débit binaire. C'est le temps nécessaire pour lire ou réécrire tout le contenu de la mémoire. Cependant, il faut signaler que l'usage de banques mémoire change la donne. Il est en effet possible de rafraichir des banques indépendantes en même temps, ce qui divise le temps de rafraichissement par le nombre de banques.

Les mémoires asynchrones à RAS/CAS : FPM et EDO-RAM

[modifier | modifier le wikicode]Avant l'invention des mémoires SDRAM et DDR, il exista un grand nombre de mémoires différentes, les plus connues étant les mémoires fast page mode et EDO-RAM. Ces mémoires n'étaient pas synchronisées par un signal d'horloge, c'était des mémoires asynchrones. Quand ces mémoires ont été créées, cela ne posait aucun problème : les accès mémoire étaient très rapides et le processeur était certain que la mémoire aurait déjà fini sa lecture ou écriture au cycle suivant. Les mémoires asynchrones les plus connues étaient les mémoires FPM et mémoires EDO.

Les mémoires FPM

[modifier | modifier le wikicode]Les mémoires FPM (Fast Page Mode) possédaient une petite amélioration, qui rendait l'adressage plus simple. Avec elles, il n'y a pas besoin de préciser deux fois la ligne si celle-ci ne changeait pas lors de deux accès consécutifs : on pouvait garder la ligne sélectionnée durant plusieurs accès. Par contre, il faut quand même préciser les adresses de colonnes à chaque changement d'adresse. Il existe une petite différence entre les mémoire FPM proprement dit et les mémoires Fast-Page Mode. Sur les premières, le signal CAS est censé passer à 0 avant qu'on fournisse l'adresse de colonne. Avec les Fast-Page Mode, l'adresse de colonne pouvait être fournie avant que l'on configure le signal CAS. Cela faisait gagner un petit peu de temps, en réduisant quelque peu le temps d'accès total.

Avec les mémoires en mode quartet, il est possible de lire quatre octets consécutifs sans avoir à préciser la ligne ou la colonne à chaque accès. On envoie l'adresse de ligne et l'adresse de colonne pour le premier accès, mais les accès suivants sont fait automatiquement. La seule contrainte est que l'on doit générer un front descendant sur le signal CAS pour passer à l'adresse suivante. Vous aurez noté la ressemblance avec le mode rafale vu il y a quelques chapitres, mais il y a une différence notable : le mode rafale vrai n'aurait pas besoin qu'on précise quand passer à l'adresse suivante avec le signal CAS.

Les mémoires FPM à colonne statique se passent même du signal CAS. Le changement de l'adresse de colonne est détecté automatiquement par la mémoire et suffit pour passer à la colonne suivante. Dans ces conditions, un délai supplémentaire a fait son apparition : le temps minimum entre deux sélections de deux colonnes différentes, appelé tCAS-to-CAS.

Les mémoires EDO-RAM

[modifier | modifier le wikicode]L'EDO-RAM a été inventée quelques années après la mémoire FPM. Elle a été déclinée en deux versions : la EDO simple, et la EDO en rafale.

L'EDO simple ajoutait une capacité de pipelining limitée aux mémoires FPM. L'implémentation n'est pas différente des mémoires FPM, si ce n'est qu'il y a un registre ajouté sur la sortie de donnée pour les lectures, un peu comme sur les mémoires SRAM synchrones. La donnée pouvait être maintenue sur le bus de données durant un certain temps, même après la remontée du signal CAS. Le registre de sortie maintenait la donnée lu tant que le signal RAS restait à 0, et tant qu'un nouveau signal CAS n'a pas été envoyé. Faire remonter le signal CAS à 1 n'invalidait pas la donnée en sortie.

La conséquence est qu'on pouvait démarrer un nouvel accès alors que la donnée de l'accès précédent était encore présent sur le bus de données. Le pipeline obtenu avait deux étages : un où on présentait l'adresse et sélectionnait la colonne, un autre où la donnée était lue depuis le registre de sortie. Les mémoires EDO étaient donc plus rapides.

Les EDO en rafale effectuent les accès à 4 octets consécutifs automatiquement : il suffit d'adresser le premier octet à lire. Les 4 octets étaient envoyés sur le bus les uns après les autres, au rythme d'un par cycle d’horloge : ce genre d'accès mémoire s'appelle un accès en rafale.

Implémenter cette technique nécessite d'ajouter un compteur, capable de faire passer d'une colonne à une autre quand on lui demande, et quelques circuits annexes pour commander le tout.

Le rafraichissement mémoire

[modifier | modifier le wikicode]Les mémoires FPM et EDO doivent être rafraichies régulièrement. Au début, le rafraichissement se faisait ligne par ligne. Le rafraichissement avait lieu quand le RAS passait à l'état haut, alors que le CAS restait à l'état bas. Le processeur, ou le contrôleur mémoire, sélectionnait la ligne à rafraichir en fournissant son adresse mémoire. D'où le nom de rafraichissement par adresse qui est donné à cette méthode de commande du rafraichissement mémoire.

Divers processeurs implémentaient de quoi faciliter le rafraichissement par adresse. Par exemple, le Zilog Z80 contenait un compteur de ligne, un registre qui contenait le numéro de la prochaine ligne à rafraichir. Il était incrémenté à chaque rafraichissement mémoire, automatiquement, par le processeur lui-même. Un timer interne permettait de savoir quand rafraichir la mémoire : quand ce timer atteignait 0, une commande de rafraichissement était envoyée à la mémoire, et le timer était reset.

Par la suite, certaines mémoires ont implémenté un compteur interne d'adresse, pour déterminer la prochaine adresse à rafraichir sans la préciser sur le bus d'adresse. Le déclenchement du rafraichissement se faisait toujours par une commande externe, provenant du contrôleur mémoire ou du processeur. Cette commande faisait passer le CAS à 0 avant le RAS. Cette méthode de rafraichissement se nomme rafraichissement interne.

On peut noter qu'il est possible de déclencher plusieurs rafraichissements à la suite en laissant le signal CAS dans le même état. Ce genre de choses pouvait avoir lieu après une lecture : on pouvait profiter du fait que le CAS soit mis à zéro par la lecture ou l'écriture pour ensuite effectuer des rafraichissements en touchant au signal RAS. Dans cette situation, la donnée lue était maintenue sur la sortie durant les différents rafraichissements.

Les mémoires SDRAM

[modifier | modifier le wikicode]Dans les années 90, les mémoires asynchrones ont laissé la place aux mémoires SDRAM, qui sont synchronisées avec le bus par une horloge. L'utilisation d'une horloge a comme avantage des temps d'accès fixes : le processeur sait qu'un accès mémoire prendra un nombre déterminé de cycles d'horloge et peut faire ce qu'il veut dans son coin durant ce temps. Avec les mémoires asynchrones, le processeur ne pouvait pas prévoir quand la donnée serait disponible et ne faisait rien tant que la mémoire n'avait pas répondu : il exécutait ce qu'on appelle des wait states en attendant que la mémoire ait fini.

Les mémoires SDRAM sont standardisées par un organisme international, le JEDEC. Le standard SDRAM impose des spécifications électriques bien précise pour les barrettes de mémoire et le bus mémoire, décrit le protocole utilisé pour communiquer avec les barrettes de mémoire, et bien d'autres choses encore. LE standard autorise l'utilisation de 2 à 8 banques dans chaque barrette de SDRAM, autorise une forme de pipeline (une commande peut démarrer avant que la précédente termine), les barrettes mémoires utilisent de l'entrelacement. Les SDRAM ont été déclinées en versions de performances différentes, décrites dans le tableau ci-dessous :

| Nom standard | Fréquence | Bande passante |

|---|---|---|

| PC66 | 66 mhz | 528 Mio/s |

| PC66 | 100 mhz | 800 Mio/s |

| PC66 | 133 mhz | 1064 Mio/s |

| PC66 | 150 mhz | 1200 Mio/s |

Le mode rafale

[modifier | modifier le wikicode]Les SDRAM gèrent à la fois l'accès entrelacé et l'accès linéaire. Nous avions vu ces deux types d'accès dans le chapitre sur les mémoires évoluées, mais faisons un bref rappel. Le mode linéaire est le mode rafale normal : un compteur est incrémenté à chaque cycle et son contenu est additionné à l'adresse de départ. Le mode entrelacé utilise un ordre différent. Avec ce mode de rafale, le contrôleur mémoire effectue un XOR bit à bit entre un compteur (incrémenté à chaque accès) et l'adresse de départ pour calculer la prochaine adresse de la rafale.

Sur les SDRAM, les paramètres qui ont trait au mode rafale sont modifiables, programmables. Déjà, on peut configurer la mémoire pour effectuer au choix des accès sans rafale ou des accès en rafale. Ensuite, on peut décider s'il faut faire un accès en mode linéaire ou entrelacé. Il y a aussi la possibilité de configurer le nombre d'octets consécutifs à lire ou écrire en mode rafale. On peut ainsi accéder à 1, 2, 4, ou 8 octets en une seule fois, alors que les EDO ne permettaient que des accès à 4 octets consécutifs.

Les délais mémoires

[modifier | modifier le wikicode]Il faut un certain temps pour sélectionner une ligne ou une colonne, sans compter qu'une SDRAM doit gérer d'autres temps d'attente plus ou moins bien connus : ces temps d'attente sont appelés des délais mémoires. La façon de mesurer ces délais varie : sur les mémoires FPM et EDO, on les mesure en unités de temps (secondes, millisecondes, micro-secondes, etc.), tandis qu'on les mesure en cycles d'horloge sur les mémoires SDRAM.

| Timing | Description |

|---|---|

| tRAS | Temps mis pour sélectionner une ligne. |

| tCAS | Temps mis pour sélectionner une colonne. |

| tRP | Temps mis pour réinitialiser le tampon de ligne et décharger la ligne. |

| tRCD | Temps entre la fin de la sélection d'une ligne, et le moment où l'on peut commencer à sélectionner la colonne. |

| tWTR | Temps entre une lecture et une écriture consécutives. |

| tCAS-to-CAS | Temps minimum entre deux sélections de deux colonnes différentes. |

Les délais/timings mémoire ne sont pas les mêmes suivant la barrette de mémoire que vous achetez. Certaines mémoires sont ainsi conçues pour avoir des timings assez bas et sont donc plus rapides, et surtout : beaucoup plus chères que les autres. Le gain en performances dépend beaucoup du processeur utilisé et est assez minime comparé au prix de ces barrettes. Les circuits de notre ordinateur chargés de communiquer avec la mémoire (ceux placés soit sur la carte mère, soit dans le processeur), doivent connaitre ces timings et ne pas se tromper : sans ça, l’ordinateur ne fonctionne pas.

Le registre de mode du contrôleur mémoire

[modifier | modifier le wikicode]Les mémoires SDRAM sont connectées à un bus mémoire spécifique, qui lui-même est commandé par un contrôleur mémoire externe. Et ce contrôleur mémoire est partiellement configurable pour les SDRAM. La configuration en question permet de gérer diverses options du mode rafale, comme le tableau ci-dessous le montre bien.

Le contrôleur mémoire interne de la SDRAM mémorise ces informations dans un registre de 10 bits, le registre de mode. Il contient un bit qui permet de préciser s'il faut effectuer des accès normaux ou des accès en rafale, ainsi qu'un autre bit pour configurer le type de rafale (normale, entrelacée). Il mémorise aussi le nombre d'octets consécutifs à lire ou écrire. Voici à quoi correspondent les 10 bits de ce registre :

| Bit n°9 | Type d'accès : en rafale ou normal |

|---|---|

| Bit n°8 et 7 | Doivent valoir 00, sont réservés pour une utilisation ultérieur dans de futurs standards. |

| Bit n°6, 5, et 4 | Latence CAS |

| Bit n°3 | Type de rafale : linéaire ou entrelacée |

| Bit n°2, 3, et 0 | Longueur de la rafale : indique le nombre d'octets à lire/écrire lors d'une rafale. |

Les commandes SDRAM

[modifier | modifier le wikicode]Le bus de commandes d'une SDRAM contient évidemment un signal d'horloge, pour cadencer la mémoire, mais pas que. En tout, 18 fils permettent d'envoyer des commandes à la mémoire, commandes qui vont effectuer une lecture, une écriture, ou autre chose dans le genre. Les commandes en question sont des demandes de lecture, d'écriture, de préchargement et autres. Elles sont codées par une valeur bien précise qui est envoyée sur les 18 fils du bus de commande. Ces commandes sont nommées READ, READA, WRITE, WRITEA, PRECHARGE, ACT, ...

| Bit CS | Bit RAS | Bit CAS | Bit WE | Bits de sélection de banque (2 bits) | Bit du bas d'adresse A10 | Reste du bus d'adresse | Nom de la commande : Description |

|---|---|---|---|---|---|---|---|

| 1 | X | Absence de commandes. | |||||

| 0 | 1 | 1 | 1 | X | No Operation : Pas d'opération | ||

| 0 | 1 | 1 | 0 | X | Burst Terminante : Arrêt d'un accès en rafale en cours. | ||

| 0 | 1 | 0 | 1 | Adresse de la banque | 0 | Adresse de la colonne | READ : lire une donnée depuis la ligne active. |

| 0 | 1 | 0 | 1 | Adresse de la banque | 1 | Adresse de la colonne | READA : lire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 1 | 0 | 0 | Adresse de la banque | 0 | Adresse de la colonne | WRITE : écrire une donnée depuis la ligne active. |

| 0 | 1 | 0 | 0 | Adresse de la banque | 1 | Adresse de la colonne | WRITEA : écrire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 0 | 1 | 1 | Adresse de la banque | Adresse de la ligne | ACT : charge une ligne dans le tampon de ligne. | |

| 0 | 0 | 1 | 0 | Adresse de la banque | 0 | X | PRECHARGE : précharge le tampon de ligne dans la banque voulue. |

| 0 | 0 | 1 | 0 | Adresse de la X | 1 | X | PRECHARGE ALL : précharge le tampon de ligne dans toutes les banques. |

| 0 | 0 | 0 | 1 | X | Auto refresh : Demande de rafraichissement, gérée par la SDRAM. | ||

| 0 | 0 | 0 | 0 | 00 | Nouveau contenu du registre de mode | LOAD MODE REGISTER : configure le registre de mode. | |

Les commandes READ et WRITE ne peuvent se faire qu'une fois que la banque a été activée par une commande ACT. Une fois la banque activée par une commande ACT, il est possible d'envoyer plusieurs commandes READ ou WRITE successives. Ces lectures ou écritures accèderont à la même ligne, mais à des colonnes différentes. Le commandes ACT se font à partir de l'état de repos, l'état où toutes les banques sont préchargées. Par contre, les commandes MODE REGISTER SET et AUTO REFRESH ne peuvent se faire que si toutes les banques sont désactivées.

Le fonctionnement simplifié d'une SDRAM peut se résumer dans ce diagramme :

Les mémoires DDR

[modifier | modifier le wikicode]Les mémoires SDRAM récentes sont des mémoires de type dual data rate, ce qui fait qu'elles portent le nom de mémoires DDR. Pour rappel, les mémoires dual data rate ont un plan mémoire deux fois plus large que le bus mémoire, avec un bus mémoire allant à une fréquence double. Par double, on veut dire que les transferts sur le bus mémoire ont lieu sur les fronts montants et descendants de l'horloge. Il y a donc deux transferts de données sur le bus pour chaque cycle d'horloge, ce qui permet de doubler le débit sans toucher à la fréquence du plan mémoire lui-même.

Les mémoires DDR sont standardisées par un organisme international, le JEDEC, et ont été déclinées en plusieurs générations : DDR1, DDR2, DDR3, et DDR4. La différence entre ces modèles sont très nombreuses, mais les plus évidentes sont la fréquence de la mémoire et du bus mémoire. D'autres différences mineures existent entre les SDRAM et les mémoires DDR.

Par exemple, la tension d'alimentation des mémoires DDR est plus faible que pour les SDRAM. ET elle a diminué dans le temps, d'une génération de DDR à l'autre. Avec les mémoires DDR2,la tension d'alimentation est passée de 2,5/2,6 Volts à 1,8 Volts. Avec les mémoires DDR3, la tension d'alimentation est notamment passée à 1,5 Volts.

Les performances des mémoires DDR

[modifier | modifier le wikicode]Les mémoires SDRAM ont évolué dans le temps, mais leur temps d'accès/fréquence n'a pas beaucoup changé. Il valait environ 10 nanosecondes pour les SDRAM, approximativement 5 ns pour la DDR-400, il a peu évolué pendant la génération DDR et DDR3, avant d'augmenter pendant les générations DDR4 et de stagner à nouveau pour la génération DDR5. L'usage du DDR, puis du QDR, visait à augmenter les performances malgré la stagnation des temps d'accès. En conséquence, la fréquence du bus a augmenté plus vite que celle des puces mémoire pour compenser.

| Année | Type de mémoire | Fréquence de la mémoire (haut de gamme) | Fréquence du bus | Coefficient multiplicateur entre les deux fréquences |

|---|---|---|---|---|

| 1998 | DDR 1 | 100 - 200 MHz | 200 - 400 MHz | 2 |

| 2003 | DDR 2 | 100 - 266 MHz | 400 - 1066 MHz | 4 |

| 2007 | DDR 3 | 100 - 266 MHz | 800 - 2133 MHz | 8 |

| 2014 | DDR 4 | 200 - 400 MHz | 1600 - 3200 MHz | 8 |

| 2020 | DDR 5 | 200 - 450 MHz | 3200 - 7200 MHz | 8 à 16 |

Une conséquence est que la latence CAS, exprimée en nombre de cycles, a augmenté avec le temps. Si vous comparez des mémoires DDR2 avec une DDR4, par exemple, vous allez voir que la latence CAS est plus élevée pour la DDR4. Mais c'est parce que la latence est exprimée en nombre de cycles d'horloge, et que la fréquence a augmentée. En comparant les temps d'accès exprimés en secondes, on voit une amélioration.

Les commandes des mémoires DDR

[modifier | modifier le wikicode]Les commandes des mémoires DDR sont globalement les mêmes que celles des mémoires SDRAM, vues plus haut. Les modifications entre SDRAM, DDR1, DDR2, DDR3, DDR4, et DDR5 sont assez mineures. Les seules différences sont l'addition de bits pour la transmission des adresses, des bits en plus pour la sélection des banques, un registre de mode un peu plus grand (13 bits sur la DDR 2, au lieu de 10 sur les SDRAM). En clair, une simple augmentation quantitative.

Avant la DDR4, les modifications des commandes sont mineures. La DDR2 supprime la commande Burst Terminate, la DDR3 et la DDR4 utilisent le bit A12 pour préciser s'il faut faire une rafale complète, ou une rafale de moitié moins de données. Mais avec la DDR4, les choses changent, notamment au niveau de la commande ACT. Avec l'augmentation de la capacité des barrettes mémoires, la taille des adresses est devenue trop importante. Il a donc fallu rajouter des bits d'adresses. Mais pour éviter d'avoir à rajouter des broches sur des barrettes déjà bien fournies, les concepteurs du standard DDR4 ont décidé de ruser. Lors d'une commande ACT, les bits RAS, CAS et WE sont utilisés comme bits d'adresse, alors qu'ils ont leur signification normale pour les autres commandes. Pour éviter toute confusion, un nouveau bit ACT est ajouté pour indiquer la présence d'une commande ACT : il est à 1 pour une commande ACT, 0 pour les autres commandes.

| Bit CS | Bit ACT | Bit RAS | Bit CAS | Bit WE | Bits de sélection de banque (2 bits) | Bit du bas d'adresse A10 | Reste du bus d'adresse | Nom de la commande : Description |

|---|---|---|---|---|---|---|---|---|

| 1 | X | Absence de commandes. | ||||||

| 0 | 0 | 1 | 1 | 1 | X | No Operation : Pas d'opération | ||

| 0 | 0 | 1 | 1 | 0 | X | Burst Terminante : Arrêt d'un accès en rafale en cours. | ||

| 0 | 0 | 1 | 0 | 1 | Adresse de la banque | 0 | Adresse de la colonne | READ : lire une donnée depuis la ligne active. |

| 0 | 0 | 1 | 0 | 1 | Adresse de la banque | 1 | Adresse de la colonne | READA : lire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 0 | 1 | 0 | 0 | Adresse de la banque | 0 | Adresse de la colonne | WRITE : écrire une donnée depuis la ligne active. |

| 0 | 0 | 1 | 0 | 0 | Adresse de la banque | 1 | Adresse de la colonne | WRITEA : écrire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 1 | Adresse de la ligne (bits de poids forts) | Adresse de la banque | Adresse de la ligne (bits de poids faible) | ACT : charge une ligne dans le tampon de ligne. | |||

| 0 | 0 | 0 | 1 | 0 | Adresse de la banque | 0 | X | PRECHARGE : précharge le tampon de ligne dans la banque voulue. |

| 0 | 0 | 0 | 1 | 0 | Adresse de la X | 1 | X | PRECHARGE ALL : précharge le tampon de ligne' dans toutes les banques. |

| 0 | 0 | 0 | 0 | 1 | X | Auto refresh : Demande de rafraichissement, gérée par la SDRAM. | ||

| 0 | 0 | 0 | 0 | 0 | 00 | Nouveau contenu du registre de mode | LOAD MODE REGISTER : configure le registre de mode. | |

Les VRAM des cartes vidéo

[modifier | modifier le wikicode]Les cartes graphiques ont des besoins légèrement différents des DRAM des processeurs, ce qui fait qu'il existe des mémoires DRAM qui leur sont dédiées. Elles sont appelés des Graphics RAM (GRAM). La plupart incorporent des fonctionnalités utiles uniquement pour les mémoires vidéos, comme des fonctionnalités de masquage (appliquer un masque aux données lue ou à écrire), ou le remplissage d'un bloc de mémoire avec une donnée unique.

Les anciennes cartes graphiques et les anciennes consoles utilisaient de la DRAM normale, faute de mieux. La première GRAM utilisée était la NEC μPD481850, qui a été utilisée sur la console de jeu PlayStation, à partir de son modèle SCPH-5000. D'autres modèles de GRAM ont rapidement suivi. Les anciennes consoles de jeu, mais aussi des cartes graphiquesn utilisaient des GRAM spécifiques.

Les mémoires vidéo double port

[modifier | modifier le wikicode]Sur les premières consoles de jeu et les premières cartes graphiques, le framebuffer était mémorisé dans une mémoire vidéo spécialisée appelée une mémoire vidéo double port. Le premier port était connecté au processeur ou à la carte graphique, alors que le second port était connecté à un écran CRT. Aussi, nous appellerons ces deux port le port CPU/GPU et l'autre sera appelé le port CRT. Le premier port était utilisé pour enregistrer l'image à calculer et faire les calculs, alors que le second port était utilisé pour envoyer à l'écran l'image à afficher. Le port CPU/GPU est tout ce qu'il y a de plus normal : on peut lire ou écrire des données, en précisant l'adresse mémoire de la donnée, rien de compliqué. Le port CRT est assez original : il permet d'envoyer un paquet de données bit par bit.

De telles mémoires étaient des mémoires à tampon de ligne, dont le support de mémorisation était organisé en ligne et colonnes. Une ligne à l'intérieur de la mémoire correspond à une ligne de pixel à l'écran, ce qui se marie bien avec le fait que les anciens écrans CRT affichaient les images ligne par ligne. L'envoi d'une ligne à l'écran se fait bit par bit, sur un câble assez simple comme un câble VGA ou autre. Le second port permettait de faire cela automatiquement, en permettant de lire une ligne bit par bit, les bits étant envoyés l'un après l'autre automatiquement.

Pour cela, les mémoires vidéo double port incorporaient un tampon de ligne spécialisé pour le port lié à l'écran. Ce tampon de ligne n'était autre qu'un registre à décalage, contrairement au tampon de ligne normal. Lors de l'accès au second port, la carte graphique fournissait un numéro de ligne et la ligne était chargée dans le tampon de ligne associé à l'écran. La carte graphique envoyait un signal d'horloge de même fréquence que l'écran, qui commandait le tampon de ligne à décalage : un bit sortait à chaque cycle d'écran et les bits étaient envoyé dans le bon ordre.

Les mémoires SGRAM et GDDR

[modifier | modifier le wikicode]De nos jours, les cartes graphiques n'utilisent plus de mémoires double port, mais des mémoires simple port. Les mémoires graphiques actuelles sont des SDRAM modifiées pour fonctionner en tant que Graphic RAM. Les plus connues sont les mémoires GDDR, pour graphics double data rate, utilisées presque exclusivement sur les cartes graphiques. Il en existe plusieurs types pendant que j'écris ce tutoriel : GDDR, GDDR2, GDDR3, GDDR4, et GDDR5. Mais attention, il y a des différences avec les DDR normales. Par exemple, les GDDR ont une fréquence plus élevée que les DDR normales, avec des temps d'accès plus élevés (sauf pour le tCAS). De plus, elles sont capables de laisser ouvertes deux lignes en même temps. Par contre, ce sont des mémoires simple port.

Les mémoires SLDRAM, RDRAM et associées

[modifier | modifier le wikicode]Les mémoires précédentes sont généralement associées à des bus larges. Les mémoires SDRAM et DDR modernes ont des bus de données de 64 bits de large, avec des d'adresse et de commande de largeur similaire. Le nombre de fils du bus mémoire dépasse facilement la centaine de fils, avec autant de broches sur les barrettes de mémoire. Largeur de ces bus pose de problèmes problèmes électriques, dont la résolution n'est pas triviale. En conséquence, la fréquence du bus mémoire est généralement moins performantes comparé à ce qu'on aurait avec un bus moins large.

Mais d'autres mémoires DRAM ont exploré une solution alternative : avoir un bus peu large mais de haute fréquence, sur lequel on envoie les commandes/données en plusieurs fois. Elles sont regroupées sous le nom de DRAM à commutation par paquets. Elles utilisent des bus spéciaux, où les commandes/adresses/données sont transmises par paquets, par trames, en plusieurs fois. En théorie, ce qu'on a dit sur le codage des trames dans le chapitre sur le bus devrait s'appliquer à de telles mémoires. En pratique, les protocoles de transmission sur le bus mémoire sont simplifiés, pour gérer le fonctionnement à haute fréquence. Le processeur envoie des paquets de commandes, les mémoires répondent avec des paquets de données ou des accusés de réception.

Les mémoires à commutation par paquets sont peu nombreuses. Les plus connues sont les mémoires conçues par la société Rambus, à savoir la RDRAM (Rambus DRAM) et ses deux successeurs XDR RAM et XDR RAM 2. La Synchronous-link DRAM (SLDRAM) est un format concurrent conçu par un consortium de plusieurs concepteurs de mémoire.

La SLDRAM (Synchronous-link DRAM)

[modifier | modifier le wikicode]Les mémoires SLDRAM avaient un bus de données de 64 bits allant à 200-400 Hz, avec technologie DDR, ce qui était dans la norme de l'époque pour la fréquence (début des années 2000). Elle utilisait un bus de commande de 11 bits, qui était utilisé pour transmettre des commandes de 40 bits, transmises en quatre cycles d'horloge consécutifs (en réalité, quatre fronts d'horloge donc deux cycles en DDR). Le bus de données était de 18 bits, mais les transferts de donnée se faisaient par paquets de 4 à 8 octets (32-65 bits). Pour résumer, données et commandes sont chacunes transmises en plusieurs cycles consécutifs, sur un bus de commande/données plus court que les données/commandes elle-mêmes.

Là où les SDRAM sélectionnent la bonne barrette grâce à des signaux de commande dédiés, ce n'est pas le cas avec la SLDRAM. A la place, chaque barrette de mémoire reçoit un identifiant, un numéro codé sur 7-8 bits. Les commandes de lecture/écriture précisent l'identifiant dans la commande. Toutes les barrettes reçoivent la commande, elles vérifient si l'identifiant de la commande est le leur, et elles la prennent en compte seulement si c'est le cas.

Voici le format d'une commande SLDRAM. Elle contient l'adresse, qui regroupe le numéro de banque, le numéro de ligne et le numéro de colonne. On trouve aussi un code commande qui indique s'il faut faire une lecture ou une écriture, et qui configure l'accès mémoire. Il configure notamment le mode rafale, en indiquant s'il faut lire/écrire 4 ou 8 octets. Enfin, il indique s'il faut fermer la ligne accédée une fois l'accès terminé, ou s'il faut la laisser ouverte. Le code commande peut aussi préciser que la commande est un rafraichissement ou non, effectuer des opérations de configuration, etc. L'identifiant de barrette mémoire est envoyé en premier, histoire que les barrettes sachent précocement si l'accès les concerne ou non.

| FLAG | CA9 | CA8 | CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Identifiant de barrette mémoire | Code de commande | ||||||||

| 0 | Code de commande | Banque | Ligne | |||||||

| 0 | Ligne | 0 | ||||||||

| 0 | 0 | 0 | 0 | Colonne | ||||||

Les mémoires Rambus

[modifier | modifier le wikicode]Les mémoires conçues par la société Rambus regroupent la RDRAM (Rambus DRAM) et ses deux successeurs XDR RAM et XDR RAM 2.

Les toutes premières étaient les mémoires RDRAM, où le bus permettait de transmettre soit des commandes (adresse inclue), soit des données, avec un multiplexage total. Le processeur envoie un paquet contenant commandes et adresse à la mémoire, qui répond avec un paquet d'acquittement. Lors d'une lecture, le paquet d'acquittement contient la donnée lue. Lors d'une écriture, le paquet d'acquittement est réduit au strict minimum. Le bus de commandes est réduit au strict minimum, à savoir l'horloge et quelques bits absolument essentiels, les bits RW est transmis dans un paquet et n'ont pas de ligne dédiée, pareil pour le bit OE. Toutes les barrettes de mémoire doivent vérifier toutes les transmissions et déterminer si elles sont concernées en analysant l'adresse transmise dans la trame.

Elles ont été utilisées dans des PC ou d'anciennes consoles de jeu. Par exemple, la Nintendo 64 incorporait 4 mébioctets de mémoire RDRAM en tant que mémoire principale. La RDRAM de la Nintendo 64 était cadencée à 500 MHz, utilisait un bus de 9 bits, et avait un débit binaire maximal théorique de 500 MB/s. La Playstation 2 contenait quant à elle 32 mébioctets de RDRAM en dual-channel, pour un débit binaire de 3.2 Gibioctets par seconde. Les processeurs Pentium 3 pouvaient être associés à de la RDRAM sur certaines mères. Les Pentium 4 étaient eux aussi associés à la de RDRAM, mais les cartes mères ne géraient que ce genre de mémoire. La Playstation 3 contenait quant à elle de la XDR RAM.

Les barrettes de mémoire DRAM

[modifier | modifier le wikicode]

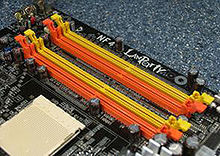

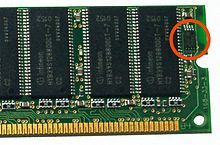

Dans les PC, les mémoires prennent la forme de barrettes mémoires. Les barrettes de mémoire se fixent à la carte mère sur un connecteur standardisé, appelé slot mémoire. Le dessin ci-contre montre une barrette de mémoire, celui-ci ci-dessous est celui d'un slot mémoire.

Le format des barrettes de mémoire

[modifier | modifier le wikicode]Sur le schéma de droite, on remarque facilement les boitiers de DRAM, rectangulaires, de couleur sombre. Chaque barrette combine ces puces de manière à additionner leurs capacités : on peut ainsi créer une mémoire de 8 gibioctets à partir de 8 puces d'un gibioctet, par exemple. Ils sont soudés sur un PCB en plastique vert sur lequel sont gravés des connexions métalliques. Certaines barrettes ont des puces mémoire d'un seul côté alors que d'autres en ont sur les deux faces. Cela permet de distinguer les barrettes SIMM et DIMM.

- Les barrettes SIMM ont des puces sur une seule face de la barrette. Elles étaient utilisées pour les mémoires FPM et EDO-RAM.

- Les barrettes DIMM ont des puces sur les deux côtés. Elles sont utilisées sur les SDRAM et les DDR.

|

|

Les trucs dorés situés en bas des barrettes de mémoire sont des broches qui connectent la barrette au bus mémoire. Les barrettes des mémoires FPM/EDO/SDRAM/DDR n'ont pas le même nombre de broches, pour des raisons de compatibilité.

| Type de barrette | Type de mémoire | Nombre de broches |

|---|---|---|

| SIMM | FPM/EDO | 30 |

| 72 | ||

| DIMM | SDRAM | 168 |

| DDR | 184 | |

| DDR2 | 214, 240 ou 244, suivant la barrette ou la carte mère. | |

| DDR3 | 204 ou 240, suivant la barrette ou la carte mère. |

Enfin, les barrettes n'ont pas le même format, car il n'y a pas beaucoup de place à l'intérieur d'un PC portable, ce qui demande de diminuer la taille des barrettes. Les barrettes SO-DIMM, pour ordinateurs portables, sont différentes des barrettes DIMM normales des DDR/SDRAM.

|

|

Les barrettes de Rambus ont parfois été appelées des barrettes RB-DIMM, mais ce sont en réalité des DIMM comme les autres. La différence principale est que la position des broches n'était pas la même que celle des formats DIMM normaux, sans compter que le connecteur Rambus n'était pas compatible avec les connecteurs SDR/DDR normaux.

Les interconnexions à l'intérieur d'une barrette de mémoire

[modifier | modifier le wikicode]Les boîtiers de DRAM noirs sont connectés au bus par le biais de connexions métalliques. Toutes les puces sont connectées aux bus d'adresse et de commande, ce qui permet d'envoyer la même adresse/commande à toutes les puces en même temps. La manière dont ces puces sont reliées au bus de commande dépend selon la mémoire utilisée.

Les DDR1 et 2 utilisent ce qu'on appelle une topologie en T, illustrée ci-dessous. On voit que le bus de commande forme une sorte d'arbre, dont chaque extrémité est connectée à une puce. La topologie en T permet d'égaliser le délai de transmission des commandes à travers le bus : la commande transmise arrive en même temps sur toutes les puces. Mais elle a de nombreux défauts, à savoir qu'elle fonctionne mal à haute fréquence et qu'elle est aussi difficile à router parce que les nombreuses connexions posent problèmes.

En comparaison, les DDR3 utilisent une topologie fly-by, où les puces sont connectées en série sur le bus de commande/adresse. La topologie fly-by n'a pas les problèmes de la topologie en T : elle est simple à router et fonctionne très bien à haute fréquence.

Les barrettes tamponnées (à registres)

[modifier | modifier le wikicode]Certaines barrettes intègrent un registre tampon, qui fait l'interface entre le bus et la barrette de RAM. L'utilité est d'améliorer la transmission du signal sur le bus mémoire. Sans ce registre, les signaux électriques doivent traverser le bus, puis traverser les connexions à l'intérieur de la barrette, jusqu'aux puces de mémoire. Avec un registre tampon, les signaux traversent le bus, sont mémorisés dans le registre et c'est tout. Le registre envoie les commandes/données jusqu'aux puces mémoire, mais le signal a été régénéré par le registre. Le signal transmis est donc de meilleure qualité, ce qui augmente la fiabilité du système mémoire. Le défaut est que la présence de ce registre fait que les barrettes ont un temps de latence est plus important que celui des barrettes normales, du fait de la latence du registre.

Les barrettes de ce genre sont appelées des barrettes RIMM. Il en existe deux types :

- Avec les barrettes RDIMM, le registre fait l'interface pour le bus d'adresse et le bus de commande, mais pas pour le bus de données.

- Avec les barrettes LRDIMM (Load Reduced DIMMs), le registre fait tampon pour tous les bus, y compris le bus de données.

Le Serial Presence Detect

[modifier | modifier le wikicode]

Toute barrette de mémoire assez récente contient une petite mémoire ROM qui stocke les différentes informations sur la mémoire : délais mémoire, capacité, marque, etc. Cette mémoire s'appelle le Serial Presence Detect, aussi communément appelé le SPD. Ce SPD contient non seulement les timings de la mémoire RAM, mais aussi diverses informations, comme le numéro de série de la barrette, sa marque, et diverses informations. Le SPD est lu au démarrage de l'ordinateur par le BIOS, afin de pourvoir configurer ce qu'il faut.

Le contenu de ce fameux SPD est standardisé par un organisme nommé le JEDEC, qui s'est chargé de standardiser le contenu de cette mémoire, ainsi que les fréquences, timings, tensions et autres paramètres des mémoires SDRAM et DDR. Pour les curieux, vous pouvez lire la page wikipédia sur le SPD, qui donne son contenu pour les mémoires SDR et DDR : Serial Presence Detect.

Les eDRAM : des DRAM adaptées aux chiplets

[modifier | modifier le wikicode]Les mémoires eDRAM, pour embedded DRAM, sont des mémoires RAM qui sont destinées à être intégrée au processeur. Pour comparer, les DRAM normales sont placées sur des barrettes de RAM ou soudées à la carte mère. Dans la quasi-totalité des cas, l'eDRAM est utilisée pour implémenter une mémoire cache, elle ne sert pas de mémoire principale (cache L4, le plus proche de la mémoire sur ces puces). De ce fait, elles sont conçues pour être très rapides, avoir une grande bande passante, au détriment de leur capacité mémoire.

Pour être plus précis, l'eDRAM est une puce de DRAM conçue pour être intégrée dans un chiplet, , à savoir des circuits imprimés qui regroupent plusieurs puces électroniques distinctes, regroupées sur le même PCB. Typiquement, un processeur de type chiplet avec de l'eDRAM comprend deux puces séparées : une pour le processeur, une autre pour une puce de communication avec la RAM. Avec la mémoire eDRAM, les deux puces sont complétées par une troisième puce spécialisée qui incorpore l'eDRAM.

Elle a été utilisée sur quelques processeurs, mais aussi dans des consoles de jeu vidéo, pour la carte graphique des consoles suivantes : la PlayStation 2, la PlayStation Portable, la GameCube, la Wii, la Wii U, et la XBOX 360. Sur ces consoles, la RAM de la carte graphique était intégrée avec le processeur graphique dans le même circuit. La fameuse mémoire vidéo et le GPU n'étaient qu'une seule et même puce électronique, un seul circuit intégré. Ce n'est pas le cas sur une carte graphique moderne : regardez votre carte graphique avec attention et vous verrez que le GPU est une puce carrée située sous les ventilateurs, alors que les puces mémoires sont situées juste autour et soudées sur le PCB de la carte.

Les processeurs Intel Core de microarchitecture Broadwell disposaient d'un cache L4 de 128 mébioctets, intégralement implémenté avec de la mémoire eDRAM. Quelques processeurs de la microarchitecture précédente (Haswell), disposaient aussi de ce cache. Le cache L4 eDRAM était implémenté sur un chiplet à part, à savoir que le processeur était composé de trois puces séparées : une pour le processeur, une autre pour la gestion des entrées-sorties, et une autre pour le cache L4. La puce pour le cache L4 était appelée Crystal Well. La puce Crystal Well était une puce gravée en 22nm, ce qui était une finesse de gravure plus élevée que celle des processeurs associés.

Crystal Well était très optimisé pour l'époque. Par exemple, elle disposait de bus séparées pour la lecture et l'écriture, chose qu'on retrouve fréquemment sur les SRAM mais qui est absent sur les mémoires DRAM actuelles. Pour le reste, elle ressemblait beaucoup aux mémoires DDR de l'époque (système de double data rate, entres autres), mais elle allait à une fréquence plus élevée que les DRAM de l'époque et avait un débit bien plus élevé, pour une consommation moindre. Crystal Well consommait entre 1 à 5 watts (1 watt en veille, 5 à pleine utilisation), pour un débit binaire de 102 GB/s et fonctionnait à 3.2 GHz.